# 陈建强 林少鑫 章国豪

# 2.5~2.7 GHz 高效率低谐波失真的功率放大器

#### 摘要

基于 InGaP/GaAs HBT 工艺设计了一款工作频段为 2.5~2.7 GHz 的高效率低谐波失真的功率放大器.该功放通过在输出匹配网络中引入多个 LC 谐振网络组合有效抑制了在负载处的高次谐波能量,进而提高了效率.仿真结果表明,该功率放大器在 4.5 V 的供电电压下,可以在 2.5~2.7 GHz 工作频率范围内实现 37.6 dB 的高增益输出,饱和输出功率可达 32 dBm 以及对应大于 36%的功率附加效率(PAE),二次和三次谐波都小于-60 dBc.

#### 关键词

功率放大器;InGaP/GaAs HBT;高效率;低谐波失真

中图分类号 TN722.75 文献标志码 A

收稿日期 2021-03-05

资助项目 国家自然科学基金(61974035) 作者简介

陈建强,男,硕士生,研究方向为射频与微波集成电路设计. 2112003003 @ mail2. gdut. edu.cn

章国豪(通信作者),男,博士,教授,研究 方向为微波、毫米波单片集成电路设计及新技 术研究.gz43811@qq.com

#### 1 广东工业大学 信息工程学院,广州,510006

# 0 引言

移动终端设备日渐广泛使用,2.5~2.7 GHz 作为时分双工-长期演进(Time Division Duplexing-Long Term Evolution, LTE-TDD)的主力频段<sup>[1]</sup>,研究提升该频段射频前端芯片性能方法的重要性不言而喻.作为无线收发系统中的核心模块,射频功率放大器在无线通信领域起着不可替代的作用.射频功率放大器位于发射链路的末端,与天线相连接<sup>[2]</sup>.在射频前端芯片中,射频功率放大器属于非线性失真最大、消耗能量和产生热量最多的器件.伴随着信息技术和半导体技术的更新换代,系统对功率放大器所提出的性能要求越来越高,高效率、高线性度已经成为射频功率放大器发展的一种趋势<sup>[3-5]</sup>.

2010年,Rasmi 等<sup>[6]</sup>基于砷化镓(GaAs)工艺设计一款功率放大器,该功放在 2.4 GHz 频率时实现 9.83 dB 的增益,在输出功率等于 14.83 dBm 时功率附加效率大于 11.73%.2017年,魏碧华等<sup>[7]</sup>基于 GaAs 增强型赝配高电子迁移率晶体管(Enhancement mode Pseudomorphic High Electronic Mobility Transistors, E-PHEMT)工艺,设计了一款应用于第五代通信和点对点传输的高性能线性功率放大器,在 9~15 GHz 频率内可以实现大于 20 dB 的小信号增益,1 dB 压缩点的输出功率不小于 27 dBm,以及实现不小于 35%的功率附加效率.2020年,毛小庆等<sup>[8]</sup>基于 GaAs PHEMT 工艺,设计了一款工作在 1.94~2.82 GHz 频带内的高效率功率放大器,实现频带内输出功率为 30.29~32.07 dBm,对应功率附加效率为 30%~41.9%,小信号增益峰值为 31.97 dB.

依据现代无线通信标准下所规定达到的性能指标要求,本文采用线性度好、功率密度高的 InGaP/GaAs 异质结双极晶体管(Heterojunction Bipolar Transistor, HBT) 工艺<sup>[9-12]</sup>设计一款工作频段为 2.5~2.7 GHz 的三级射频功率放大器.本设计以三级放大器结构实现了37.6 dB 的高增益,设计的三陷波输出匹配网络在二次谐波频段5.0~5.4 GHz 内的抑制都小于-60 dBc,提供了一个较宽的二次谐波抑制频段.另外,该电路利用自适应偏置网络提高线性度,改善增益压缩和相位失真.

#### 1 整体电路结构

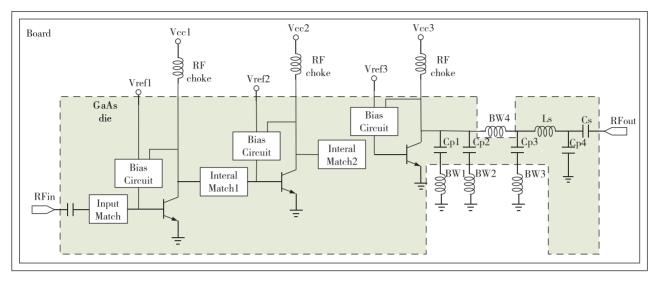

本文所设计的射频功率放大器电路拓扑结构如图 1 所示.虚线框

图 1 整体功放结构

Fig. 1 The top PA structure

内为片上电路,通过键合金线与印刷电路板(Printed Circuit Board, PCB)进行连接.该模块采用三级放大管子作为主体电路,确保输出足够高的增益.其中第一级管子偏置在A类状态,第二级和第三级管子分别偏置在浅AB类和深AB类状态,以保证增益、线性度和效率的折中.同时,三级放大器管子均采用自适应偏置电路.特别地,为了确保低谐波失真,输出匹配网络实现了较宽的谐波陷波效果.

### 2 电路设计

#### 2.1 自适应偏置网络的设计

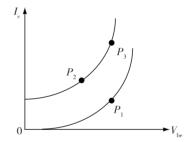

对于 HBT 晶体管来说,由于发射区与基区所形成的发射结对正向电压具有钳制的作用,但对负向电流会产生截断,因此当功率放大器的输入信号幅度超过一定限制时,发射结电压  $V_{be}$ 将受到钳制,而电流  $I_{B}$ 也会出现截断现象.具体表现为正弦电压的正向部分和正弦电流的负向部分出现失真,利用傅里叶变换将失真信号在频域维度内展开,可以发现管子的电流直流部分会因此增加,而电压的直流部分会因此减少.如图 2 所示,这样直接导致原本设定的偏置点出现偏移现象,从  $P_{1}$  点移动到  $P_{2}$  点,造成管子的跨导发生变化,提前发生增益压缩现象.因此,对于大信号功率放大器来说,偏置网络需要进行自动补偿跨导的减少量,将偏置点从  $P_{2}$  点移动到  $P_{3}$  点.

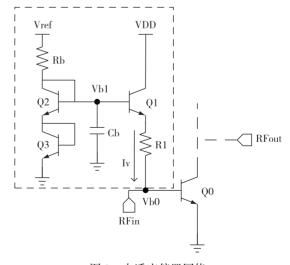

本次设计采用自适应偏置网络 $[^{13-14}]$ ,如图 3 所示,虚线框内为自适应偏置网络,为晶体管  $Q_0$  提供

图 2 HBT 晶体管的转移特性曲线

Fig. 2 Transfer characteristic curve of HBT transistor

图 3 自适应偏置网络

Fig. 3 Adaptive bias network

直流偏置.其中晶体管  $Q_1$  和  $Q_2$  组成电流镜结构,晶体管  $Q_3$  使得电流镜的左右电路支路的器件电压维

持正常工作水平, 电流镜的静态输出电流  $I_v$  由  $V_{ref}$ 、电阻  $R_b$  和  $R_1$ , 以及晶体管  $Q_0$ 、 $Q_1$ 、 $Q_2$ 、 $Q_3$  所决定.

当晶体管  $Q_0$  基极加输入信号时,一部分射频信号将会通过电阻  $R_1$  经管子  $Q_1$  和电容  $C_b$  通路泄露到地,电容  $C_b$  降低了该通路的交流阻抗.虽然这在一定程度上消耗了一小部分输入信号的能量,但是同时也改善了增益压缩和相位失真的情况,进而优化了电路整体线性度.伴随着晶体管  $Q_0$  基极的输入信号不断增大,因为晶体管  $Q_0$  和  $Q_1$  的发射结都具有相同的器件特性,而且电容  $C_b$  的存在使得晶体管  $Q_1$  基极直流电位是固定的,则晶体管  $Q_0$  的基极电位可以表达为

$$V_{\text{be } \rho_0} = V_{\text{b}0_1} - I_{\text{v}} R_1 - V_{\text{be } \rho_1} . \tag{1}$$

可以看出由于晶体管  $Q_0$  和晶体管  $Q_1$  的相同特性致使电势差  $V_{\text{be},Q_0}$  和  $V_{\text{be},Q_1}$  在大信号下的变化趋势一样,当发生电压钳位时,晶体管  $Q_1$  发射结电势差  $V_{\text{be},Q_1}$  的减少将减缓晶体管  $Q_0$  发射结电势差  $V_{\text{be},Q_0}$  的降低,补偿了晶体管  $Q_0$  基极的电位,相当于补偿了降低的跨导.因此,该电路结构从一定程度上对增益压缩和相位失真提供了改善措施,提高了系统的线性度.

另外,电阻  $R_1$  的存在也使得偏置网络具备负反馈功能,以抑制静态电流随温度的波动,降低了温度对所设计系统的影响.

#### 2.2 输出匹配网络的设计

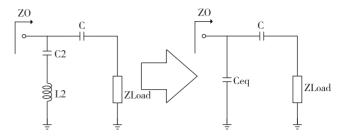

对于偏置在 Class AB 状态的功率放大器来说,电路整体效率随着导通角的降低而升高,与此同时输出信号中谐波分量的占比也增大,特别地,在导通角  $\alpha>\pi$  的阶段以二次谐波分量的影响最为主要.因此,在功率级电路的输出端口设计谐波抑制电路是必不可少的 $^{[15]}$ .本设计采用多个串联谐振电路对系统的二次谐波和三次谐波进行抑制.如图 4 所示,电容  $C_2$  和电感  $L_2$  构成串联谐振电路,在二次谐波附近表现为短路状态,而在工作频率带宽内则表现为高阻抗,从而使得只有输出信号中的基频信号传输到负载  $Z_{Local}$ .

图 4 右图为基波等效电路,其中电容  $C_{\text{eq}}$ 在基频  $f_0$  下的阻抗为

$$Z_{C_{\text{eq}}} = -j \left( \frac{1}{2\pi f_0 C_2} - 2\pi f_0 L_2 \right) . \tag{2}$$

根据电容  $C_2$  和电感  $L_2$  的谐振频率为  $2f_0$  ,则

$$2f_0 = \frac{1}{2\pi\sqrt{L_2C_2}}. (3)$$

图 4 谐振电路及其基波等效电路

Fig. 4 Resonant circuit and its equivalent circuit of the fundamental wave

因此可以得到:

$$Z_{C_{\rm eq}} = -j \left( \frac{1}{\frac{4}{3} \times 2\pi f_0 C_2} \right). \tag{4}$$

所以可以计算得到谐振电容  $C_2$  和谐振电感  $L_2$  为

$$C_2 = \frac{3}{4} C_{\text{eq}} , \qquad (5)$$

$$L_2 = \frac{1}{(4\pi f_0)^2 C_2}.$$

(6)

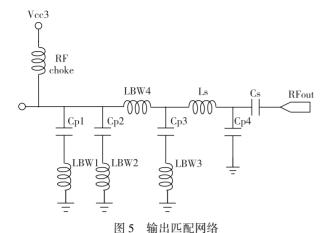

在本设计中,输出匹配网络实现了 3 个由串联 LC 组合组成的谐振电路,如图 5 所示,其中包括电容  $C_{\rm pl}$  和电感  $L_{\rm BW_1}$  、电容  $C_{\rm p2}$  和电感  $L_{\rm BW_2}$  构成的 2 个串联谐振电路,它们分别在二次谐波附近以不同的频率谐振,电容  $C_{\rm pl}$  和电感  $L_{\rm BW_1}$  谐振于 5 GHz,用以抑制电路输出二次谐波中的较低频点,电容  $C_{\rm p2}$  和电感  $L_{\rm BW_2}$  谐振于 5.4 GHz,用以抑制电路输出二次谐波中的较高频点,因此组成了在宽频率范围内的二次谐波杂散输出的抑制电路. 另外,电容  $C_{\rm p3}$  和电感  $L_{\rm BW_3}$  构成第 3 个串联谐振电路,用于抑制电路输出的三次谐波,这使得无需在发射链路中进行额外的谐波滤波.

上述 3 个谐振电路都可等效成为基频处的电容,考虑到良好的输出带宽,提高整体电路 Q 值.如图 5 所示,输出匹配电路采用 2 个级联 L 型低通匹配网络进行设计,结合谐波抑制电路一起构成整个输出匹配网络.因此,可以实现具有谐波滤波的紧凑输出匹配网络,从而减小了系统的尺寸、成本和功耗.

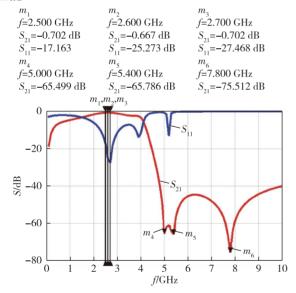

图 6 展示了输出匹配网络仿真所得的反射系数和传输系数与频率之间的关系. 该输出匹配网络在工作频段 2.5~2.7 GHz 内的插入损耗在 0.7 dB 以内,而且所设计的谐振电路在 5.0 GHz 和 5.4 GHz

Fig. 5 Output match network

附近产生两个抑制点,使得在二次谐波频段 5.0~5.4 GHz 内的抑制都低于-60 dB,提供了一个较宽的二次谐波抑制频段,保证了低谐波失真性能;另外,在三次谐波频率处也实现了很好的谐波抑制性能.

图 6 输出匹配网络仿真结果

Fig. 6 Simulation result of the output match network

#### 3 仿真结果

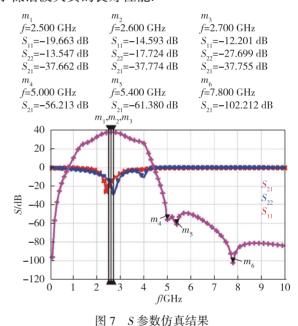

本设计采用三级放大器架构搭建了工作频段为 2.5~2.7 GHz 的射频功率放大器,采用 4.5 V 的供电电压以及 2.85 V 的参考电压,综合考虑功率放大器的最大输出功率和增益水平,最终确定三级放大器管子的静态电流分别为 26、55 和 141 mA.利用 ADS (Advanced Design System)对片上绕线电感进行电磁(Electromagnetic,EM)仿真,整体电路经过调谐

后,得到小信号 S 参数仿真结果如图 7 所示,在2.5~2.7 GHz 工作频段内所测得功率放大器的小信号增益  $S_{21}$  在 37.6~37.8 dB 之间,输入回波损耗  $S_{11}$  均小于-12 dB,输出回波损耗  $S_{22}$  均小于-13 dB,表明该电路小信号性能较好.同时,在 5.0~5.4 GHz 的二次谐波频段内  $S_{21}$  均小于-50 dB,在三次谐波频率处  $S_{21}$  均小于-80 dB,实现了较好的谐波抑制性能.

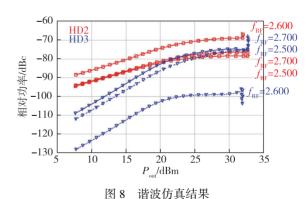

图 8 展示了本设计的功率放大器谐波性能仿真结果,其中: $P_{\text{out}}$ 表示输出功率,单位为 dBm; HD2 和 HD3 分别表示二次和三次谐波的相对功率,单位为 dBc; $f_{\text{RF}}$ 表示输入信号的频率,单位为 GHz.根据仿真结果可以看出二次和三次谐波都小于-60 dBc,实现了低谐波失真的良好性能.

Fig. 7 Simulation result of the S-parameters

Fig. 8 Simulation result of the harmonic

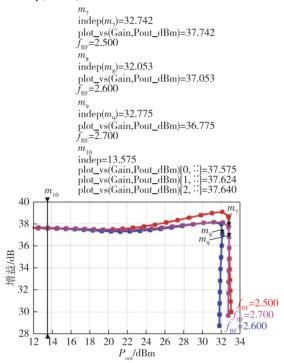

图 9 给出了功率放大器的大信号增益仿真结果,可以看出该功率放大器的大信号增益在 37.6 dB

左右,实现了较高的增益水平,1-dB 压缩点的输出功率大于32 dBm.

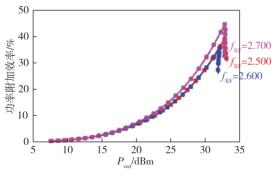

图 10 为功率附加效率的仿真结果,在 2.5~2.7 GHz 内该功率放大器能实现 32 dBm 的饱和输出功率以及对应大于 36%的功率附加效率(Power Added Efficiency, PAE).

图 9 增益仿真结果

Fig. 9 Simulation result of gain

图 10 功率附加效率仿真结果

Fig. 10 Simulation result of PAE

#### 4 结束语

针对 2.5~2.7 GHz 的工作频段,本文设计了一款三级功率放大器架构,利用自适应偏置网络提供直流偏置点,在输出匹配网络上实现一个较宽的二次谐波抑制频段,通过 ADS 仿真结果表明所设计功

率放大器可以实现 32 dBm 的饱和输出功率以及对应大于 36%的功率附加效率(PAE),以及二次和三次谐波都小于-60 dBc 的良好谐波抑制性能.

## 参考文献

#### References

- [1] 王浩年,刘冰婷.TD-LTE F 频段和 D 频段组网对比分析研究[J].中国新通信,2017,19(18):27-28 WANG Haonian, LIU Bingting. Comparative analysis of TD-LTE F-band and D-band networking[J]. China New Telecommunications, 2017, 19(18):27-28

- [2] 胡荣贻,韩潇,范斌.终端射频前端架构浅析[J].邮电设计技术,2017(9):14-18 HU Rongyi, HAN Xiao, FAN Bin. Initial analysis of RF front-end design for mobile phone [J]. Designing Techniques of Posts and Telecommunications, 2017(9):14-18

- [ 3 ] Zhang G, Khesbak S, Agarwal A, et al. Evolution of RFIC handset PAs [ J ]. IEEE Microwave Magazine, 2010, 11 (1):60-69

- [4] Li Y, Zhu R, Prikhodko D, et al. LTE power amplifier module design: challenges and trends [C] // 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology. November 1 - 4, 2010, Shanghai, China. IEEE, 2010; 192-195

- [5] Refai W Y.A linear RF power amplifier with high efficiency for wireless handsets [D]. Blacksburg: Virginia Polytechnic Institute and State University, 2014

- [ 6 ] Rasmi A, Marzuki A, Nizam Osman M, et al. Development of 2.4 and 3.5 GHz 0.15 μm GaAs PHEMT medium-power amplifier employing core-based design approach [ J ]. Microelectronics International, 2010, 27(1):25-32

- [7] 魏碧华,蔡道民,武继斌.9~15 GHz GaAs E-PHEMT 高性能线性功率放大器[J].半导体技术,2017,42 (7):489-492,498 WEI Bihua, CAI Daomin, WU Jibin.9-15 GHz GaAs E-PHEMT high performance linear power amplifier[J].

- Semiconductor Technology, 2017, 42(7):489-492, 498 [8] 毛小庆, 何勇畅, 陈志巍, 等. 一种 0.15 μm GaAs pHEMT 高效率功率放大器 [J]. 微电子学, 2020, 50 (4):499-502,508

- MAO Xiaoqing, HE Yongchang, CHEN Zhiwei, et al. A 0. 15 μm GaAs pHEMT high efficiency power amplifier [J]. Microelectronics, 2020, 50(4):499-502, 508

- [ 9 ] Wei Y, Staudinger J, Miller M. High efficiency linear GaAs MMIC amplifier for wireless base station and Femto cell applications [C] // 2012 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications. January 15 18, 2012, Santa Clara, CA, USA. IEEE, 2012:49-52

- [10] 高思鑫,张晓朋,高博,等.基于 InGaP/GaAs HBT 的高效率高谐波抑制功率放大器[J].半导体技术,2020,45(12):957-963 GAO Sixin,ZHANG Xiaopeng,GAO Bo,et al.High effi-

- GAO Sixin, ZHANG Xiaopeng, GAO Bo, et al. High efficiency and high harmonic suppression power amplifier based on InGaP/GaAs HBT[J]. Semiconductor Technology, 2020, 45(12):957-963

- [11] Nellis K, Zampardi P J. A comparison of linear handset power amplifiers in different bipolar technologies [J]. IEEE Journal of Solid-State Circuits, 2004, 39 (10): 1746-1754

- [12] 高鵬坤.基于 TD-LTE 的 GaAs HBT 功率放大器及线性化技术研究[D].北京:北京工业大学,2015 GAO Pengkun. Research on power amplifier and linearization techniques based on TD-LTE and GaAs HBT technology [D]. Beijing: Beijing University of Technology,2015

- [13] 彭林,李嘉进,梁钊铭,等.基于 LC 巴伦的伪差分功率

- 放大器设计[J].电子技术应用,2020,46(8):9-12 PENG Lin, LI Jiajin, LIANG Zhaoming, et al. Design of pseudo-differential power amplifier based on LC balun [J].Application of Electronic Technique, 2020,46(8): 9-12

- [ 14 ] Baek S, Ahn H, Nam I, et al. A linear InGaP/GaAs HBT power amplifier using parallel-combined transistors with IMD3 cancellation [ J ]. IEEE Microwave and Wireless Components Letters, 2016, 26(11):921-923

- [15] Cripps S C.RF power amplifiers for wireless communications [J].IEEE Microwave Magazine, 2000, 1(1):64

# A 2.5-2.7 GHz power amplifier with high efficiency and low harmonic distortion

CHEN Jianqiang LIN Shaoxin ZHANG Guohao School of Information Engineering, Guangdong University of Technology, Guangzhou 510006

**Abstract** A 2.5-2.7 GHz Power Amplifier (PA) with high efficiency and low harmonic distortion in InGaP/GaAs HBT technology is designed. Multiple LC tanks are introduced into the output matching network of the presented PA to suppress the high-order harmonic distortions and improve efficiency. The simulation results show that, the PA achieves a high gain of 37.6 dB and a saturated output power of 32 dBm with Power Added Efficiency (PAE) of 36% at the saturated situation. The second and the third harmonic are both less than -60 dBc.

Key words power amplifier; InGaP/GaAs HBT; high efficiency; low harmonic distortion